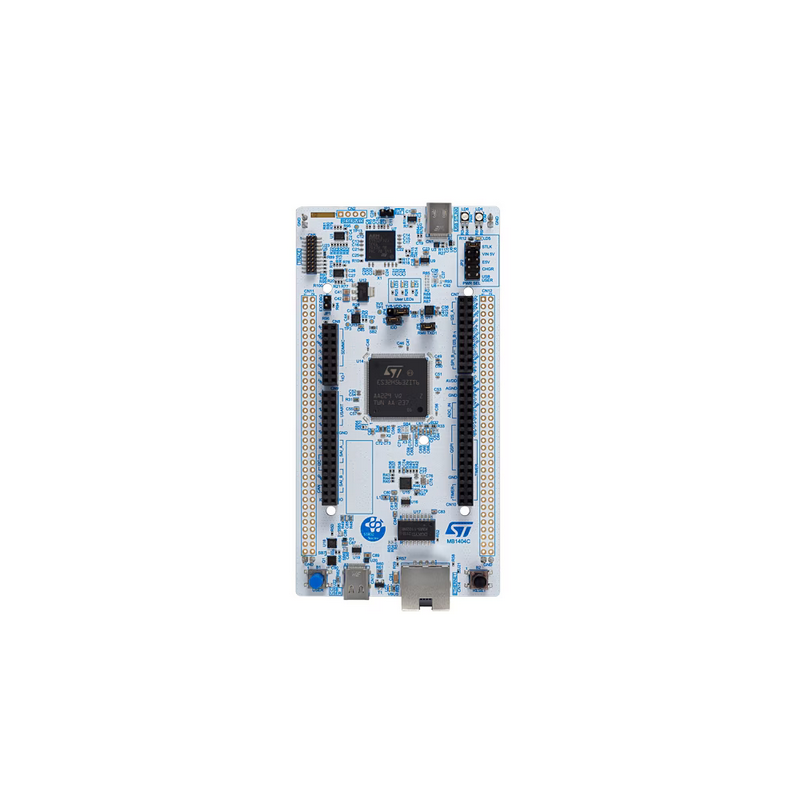

The NUCLEO-H563ZI is a Nucleo-144 form factor development board designed to simplify prototyping with high-performance STM32 microcontrollers. It features the powerful STM32H563ZI MCU, based on the 250 MHz Arm Cortex-M33 core, offering an excellent balance between energy efficiency and processing power.

This board is ideal for projects requiring robust security (TrustZone architecture), digital signal processing (DSP), or complex IoT applications. It provides Arduino (Zio connector) and Morpho connectivity for easy access to I/O pins, along with a built-in ST-Link/V3SE programmer for debugging and reprogramming.

You might also like